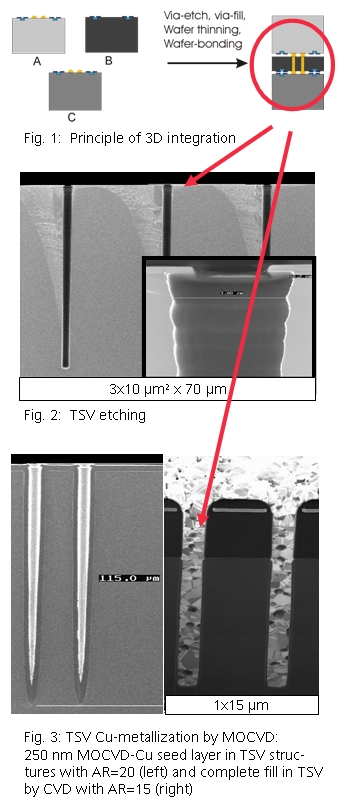

3D-Integration

Die 3D-Integration ist von großem Interesse für verschiedene Einsatzmöglichkeiten auf den Gebieten der Mikroelektronik und der MEMS-Technologie. Hierbei werden Chips zur Verringerung der elektrischen Weglängen vertikal übereinander gestapelt, um folglich die elektrische und thermische Leistungsfähigkeit zu erhöhen und die Größe der Chips zu minimieren. Andererseits eröffnet sich durch 3D-Integration die Möglichkeit, Bauelemente verschiedener Funktion und Technologie zu integrieren, z.B. MEMS-Bauelemente mit der entsprechenden Ansteuer- und Auswerteelektronik. Die Fertigungstechnologie umfasst beispielsweise Waferdünnen, Strukturierung und Füllung von Durchkontaktierungen (Through-Silicon-Via = TSV) sowie Wafer- oder Chipbonden.

Forschung und Entwicklung

Wir arbeiten bereits seit mehreren Jahren auf dem Gebiet der 3D-Integration. Unser Hauptaugenmerk liegt dabei auf der Entwicklung von TSV-Ätzprozessen und TSV-Metallisierung. Das Fraunhofer ENAS wirkt während der gesamten Prozesskette eng mit dem Fraunhofer IZM Berlin, dem IZM-ASSID Dresden und dem EMFT München zusammen.

TSV-Ätzen

Die Geometrie der TSVs hat großen Einfluss auf das nachfolgende Füllen mit leitfähigen Materialien. Wir entwickeln Ätzprozesse für optimierte Profilbohrungen, wie kegelförmige Durchbrüche.

- Aspektverhältnisse bis zu 9

- kleinste TSV-Größen 3x10 µm² mit Tiefen bis zu 70 µm

- Tapered-Via-Öffnungen mit 86° Böschungswinkel

TSV-Metallisierung

Das Metallisierungsschema ist das folgende:

- MOCVD TiN

- Abscheiden der Haftschicht (TiN based)

- In situ MOCVD Cu (CupraSelect™)

TSVs mit Durchmessern kleiner als 3 µm können vollständig mit Kupfer-CVD gefüllt werden. Für TSVs mit größerem Durchmesser wird Cu-MOCVD genutzt, um Seed Layer für die Kupfergalvanik abzuscheiden. Die Resultate aller Abscheidungsprozesse sind stark von der Geometrie und der Tiefe der TSVs sowie der Strukturdichte abhängig. Die Durchführungen sollten für jedes TSV-Layout optimiert werden, um einen bestmöglichen Ausgleich zwischen Abscheiderate und Kantenbedeckung zu schaffen.

Anlagentechnik

- Applied Materials P5000 für Barriere- und Cu-CVD

- Applied Materials P5000 DCVD (PECVD SiO2, SiN, SiC:H, SiCN:H, PE-TEOS, TEOS/Ozone)

- STS DRIE Ätzanlage (Tiefes Si-Ätzen)

- Applied Materials Mirra für Barriere- und Cu-CMP

- IPEC 472 für Si- und SiO2-CMP

Prozesse

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme