UNSETH: Prozess und Zuverlässigkeitsbewertungen von Integrations- und Verpackungstechnologien, die hardwarebasierte Sicherheit zur Verfügung stellen

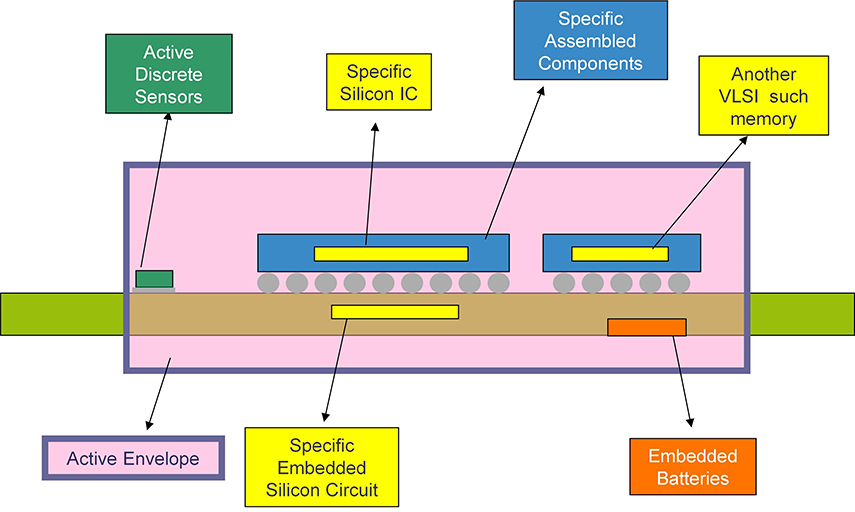

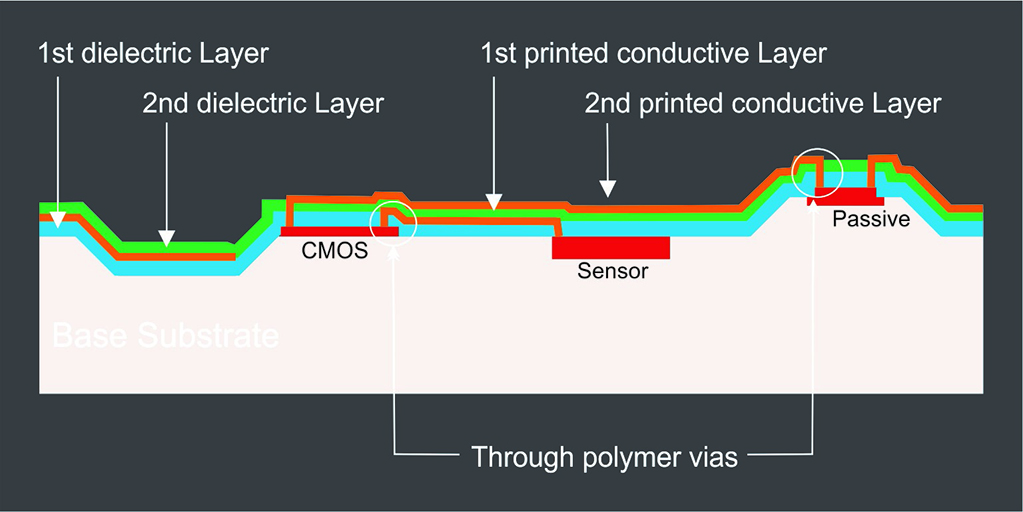

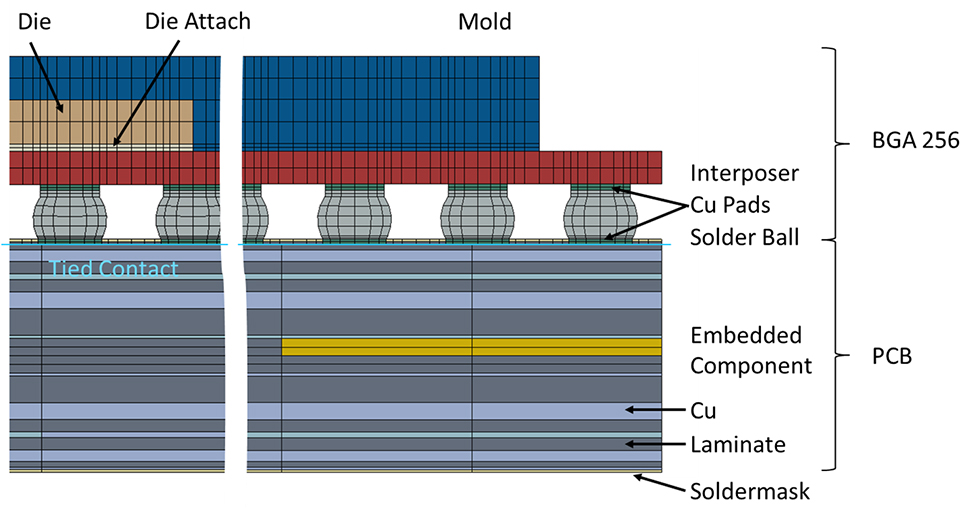

Das Projekt UNSETH (FP7-SEC GA N°312701) entwickelt unter Leitung von Thales TCS/TGS und Mitarbeit von Fraunhofer ENAS, Nanium und Epoche & Espri eine neue Generation von Schutzmaßnahmen für elektronische Schaltungen. Vorhandene Lösungen auf Chiplevel werden durch Packaging- und AVT-Lösungen ergänzt, die die Einbettung aktiver Komponenten wie Mikrocontroller und Waferlevel-Packages sowie Lagen mit Netzstruktur und in Aerosoldruck von silbernanopartikelhaltigen Tinten hergestellten Abdeckungen für sichere Leiterplattenbereiche umfassen. Zur Realisierung der Sensorstruktur in der aktiven Kappe als auch als Umverdrahtung für die 3D-Integration wurde am Fraunhofer ENAS ein Multilagenaufbau entwickelt, bei dem ein Parylen-Dielektrikum die leitenden Silberstrukturen trennt und Durchkontaktierungen durch Laserablation hergestellt werden. Die Prozessentwicklung beinhaltet die Optimierung des Druck- und Sinterprozesses, der Vorbehandlungsschritte, des Laserbohrens und des Viafills. Um den Anforderungen an die Robustheit der sicheren Elektronik genügen zu können, werden die Entwicklungen von umfangreichen numerischen und experimentellen Zuverlässigkeitsunter-suchungen begleitet.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme