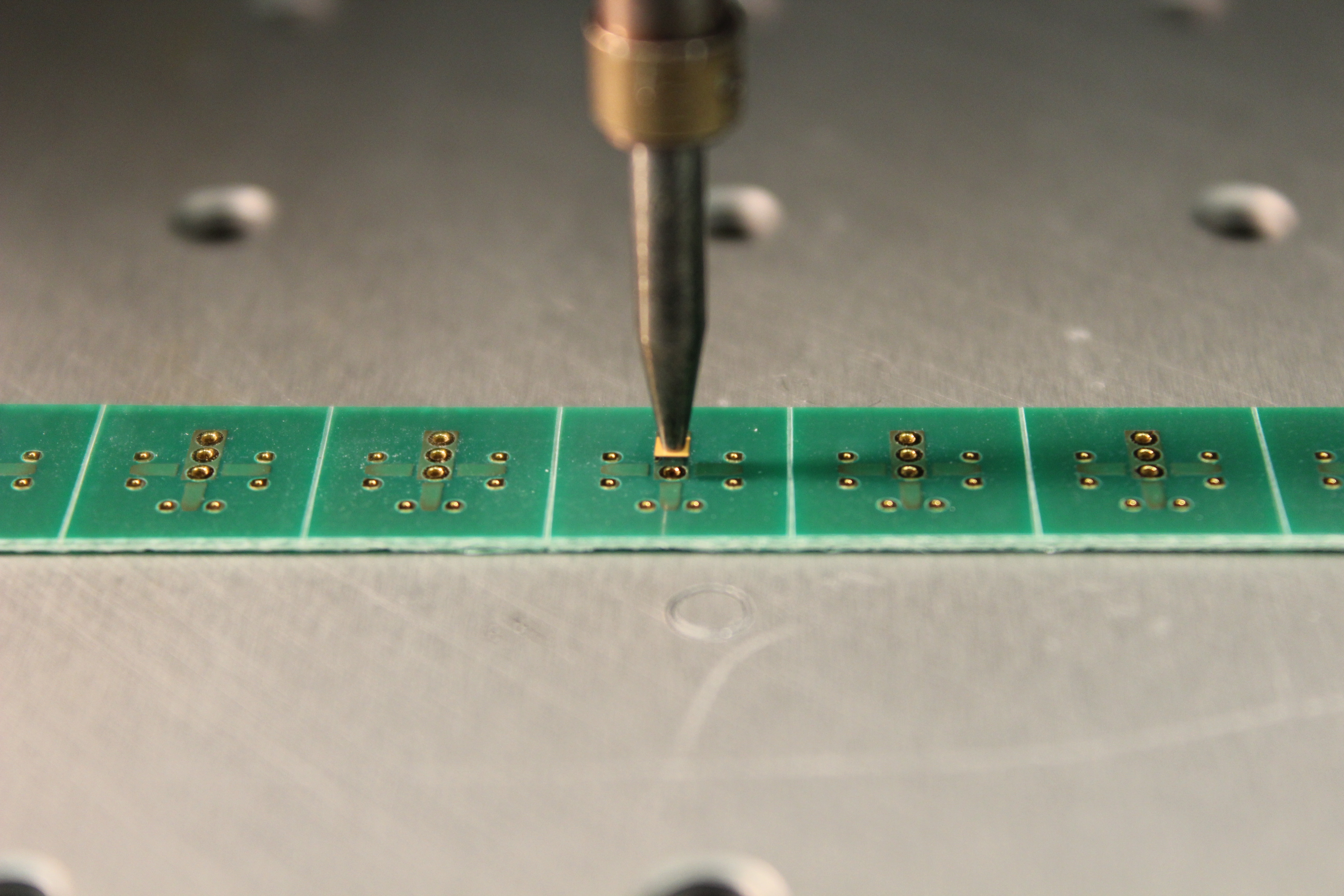

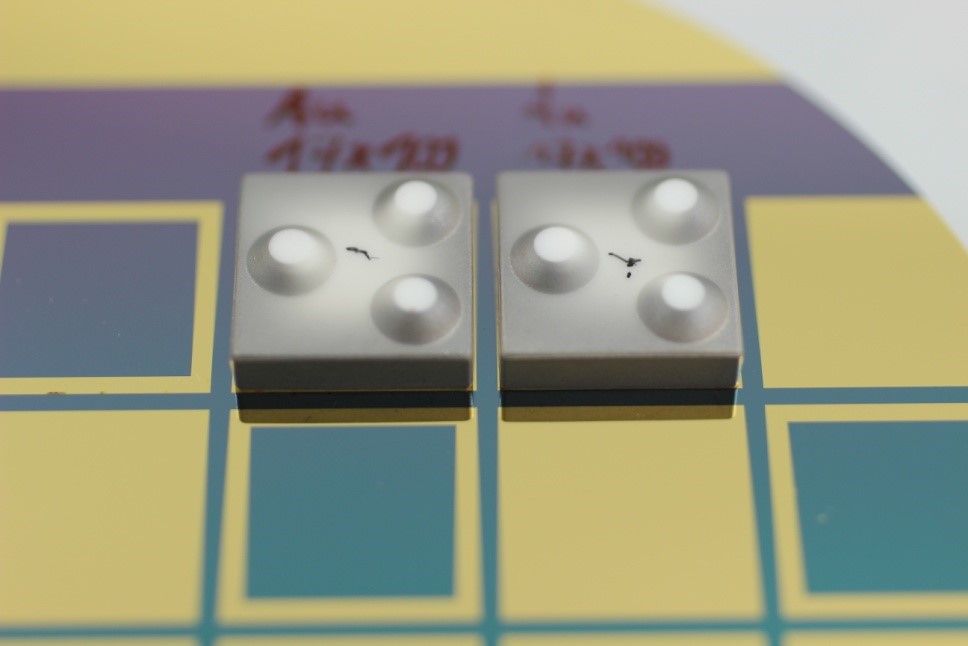

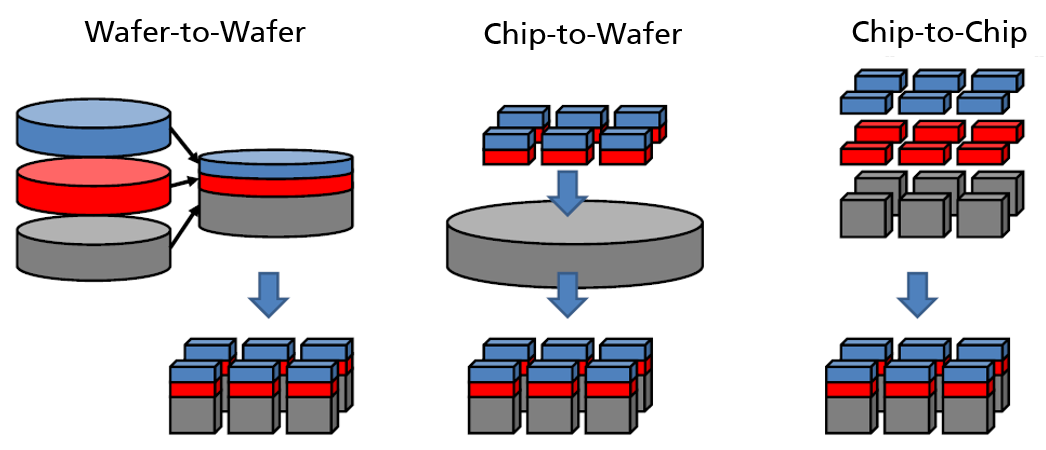

Gewöhnlich werden die Funktionsblöcke in einem Package zweidimensional (2D) integriert oder auf eine Leiterplatte montiert. Nimmt man die dritte Dimension (3D) zu Hilfe, können diese Funktionsblöcke vertikal gestapelt werden, wobei jeder dieser Blöcke eine separate Ebene bildet. Jede Ebene wird dabei mittels vertikaler Verbindungen kontaktiert. Durch die 3D-Integration wird der Formfaktor, d.h. die Abmessungen in x- und y-Richtung, des Systems reduziert. Die Abmessung in z-Richtung bleibt meist vernachlässigbar klein. Das Packaging kann dabei prinzipiell auf Wafer-to-Wafer-, Chip-to-Wafer oder Chip-to-Chip-Ebene erfolgen.

Aktuell angewendete Packaging-Konzepte auf Chip-to-Chip- oder Chip-to-Wafer-Ebene werden kommerziell in Produkten wie Smart Phones, Kameras oder Laptops angewendet. Durch steigende Bedürfnisse der Hersteller elektronischer Systeme, wird eine optimale Kombination aus Funktionalität, Performance, Zuverlässigkeit und Preis gefordert. Dabei spielen auch die geometrischen Abmessungen der Systeme eine entscheidende Rolle.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme