Cool PoD: Gedruckte 3D Chip-2-Board Interconnects

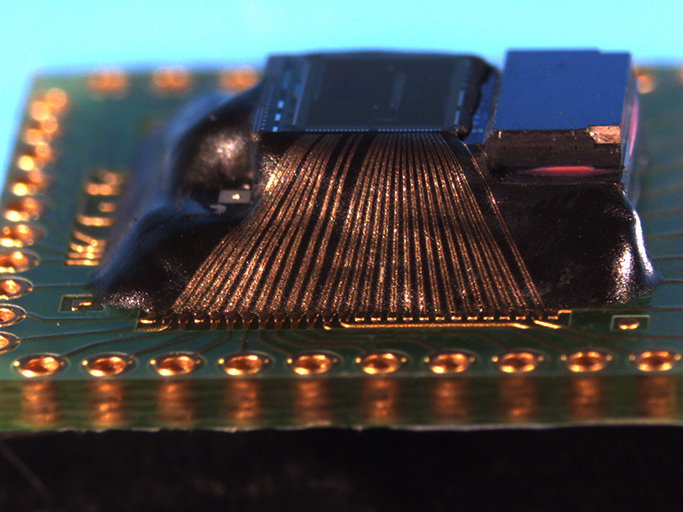

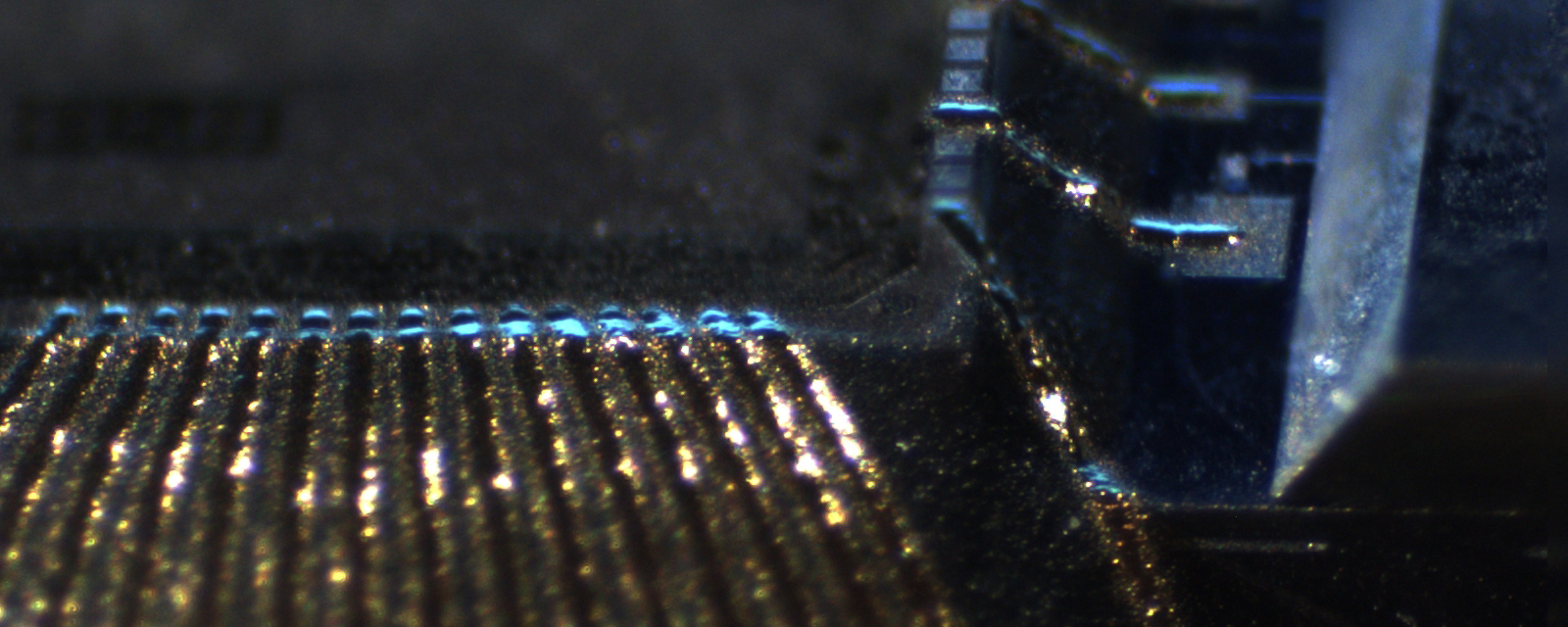

Das Projekt CoolPod hatte zum Ziel, den technischen Nachweis der Machbarkeit eines mikromechanischen Power-Down-Interrupt-Generators (PDIG) zu erbringen. Der Wandler kann aufgrund mechanischer Bewegungen elektronische Mikrosysteme aus dem sogenannten Power-Down-Mode wecken, um dadurch im Vergleich zu bestehenden Lösungen Energie in signifikantem Umfang einzusparen. Einen weiteren Schwerpunkt bildeten Untersuchungen zu einer dreidimensionalen Packagingtechnologie für Sensorik und Application-Specific-Integrated-Circuit (ASIC). PDIG, ASIC und Sensor müssen in geeigneter Weise in einem Gehäuse kombiniert und sowohl mechanisch als auch elektrisch verbunden werden. Ein weiteres wissenschaftlich-technisches Arbeitsziel war die Entwicklung neuer Packaging-Ansätze. Hierzu sollten neue Kontaktierungsmethoden beitragen, die durch Drucken von Leitbahnen über dreidimensionale Oberflächenstrukturen erfolgten. Die Substitution von Drahtbondkontakten durch gedruckte Leitbahnen unter Nutzung des Aerosol-Jet-Verfahrens war das zentrale Forschungsthema des Fraunhofer ENAS im Projekt. Durch Stapeln der Einzelchips und das Drucken wurde eine kleinstmögliche Bauform erreicht.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme