Galvanische Abscheidung

Die galvanische Abscheidung, auch elektrochemische Abscheidung (ECD) genannt, von Metallen und Metalllegierungen wird in der Mikroelektronik und MEMS-Technologie als Ergänzung zu CVD- und PVD-Prozessen genutzt. Mit Hilfe dieser nasschemischen Abscheidemethode können Schichten im Bereich ein bis mehrere zehn Mikrometer realisiert werden. Gemeinsam mit dem ZfM der TU Chemnitz arbeitet das Fraunhofer ENAS auf dem Gebiet im Rahmen von Grundlagenforschung, angewandten Forschung und an Industrieprojekten.

Forschung und Entwicklung

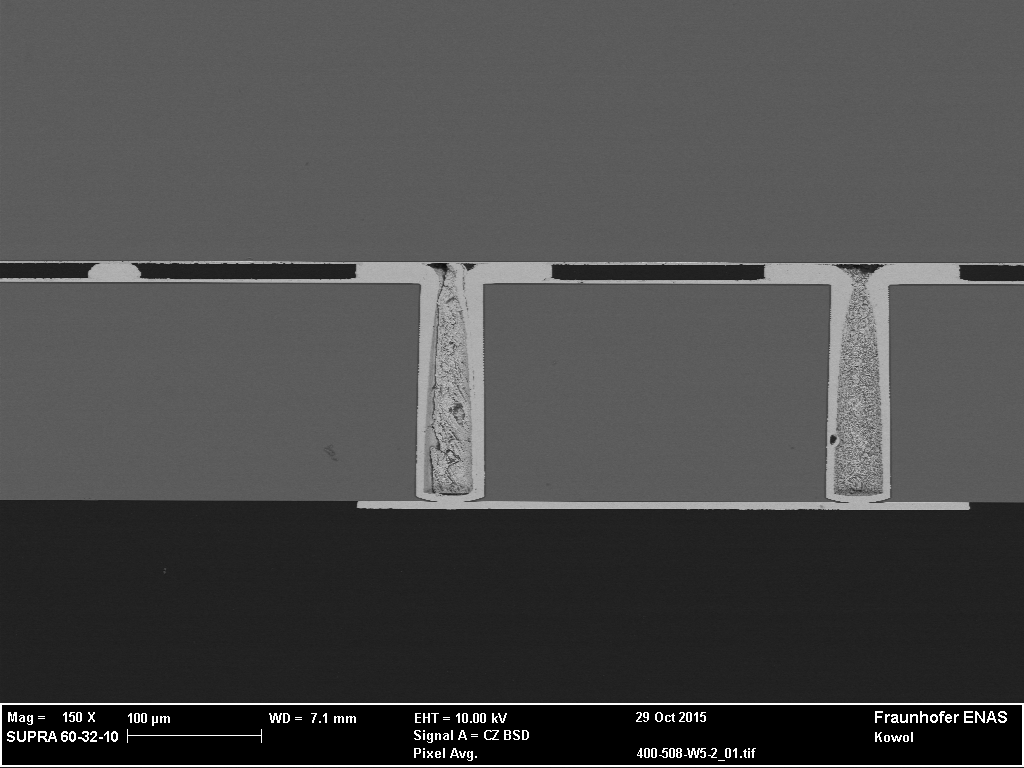

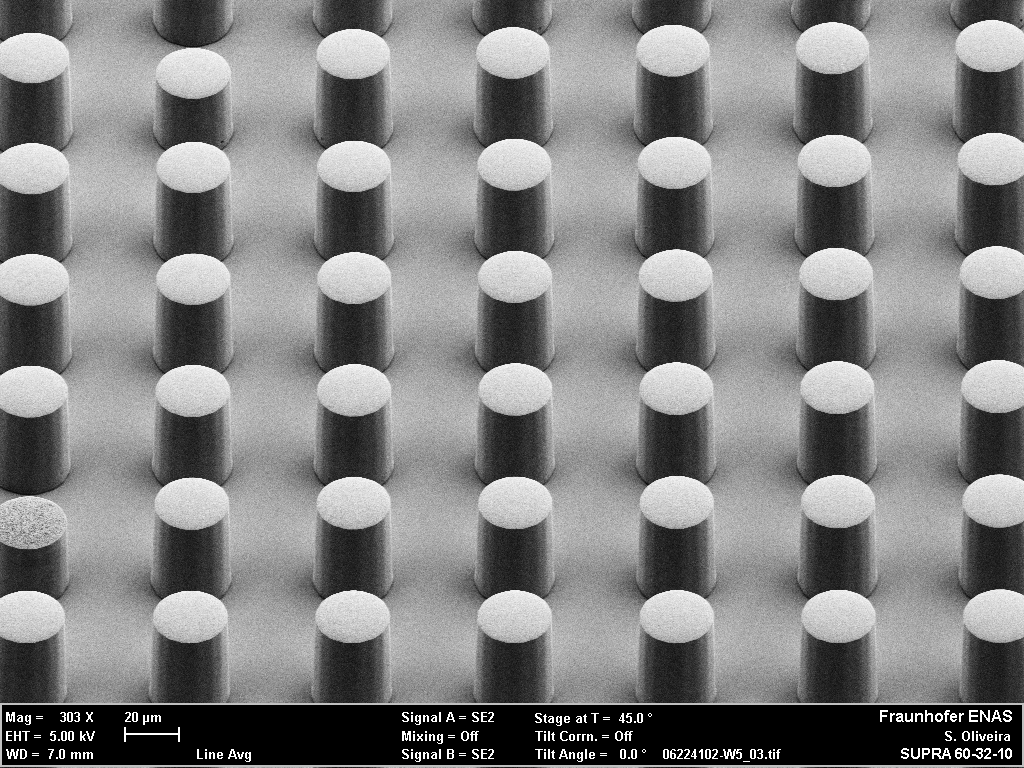

Die ECD wird häufig genutzt, um verhältnismäßige dicke Metallisierungen herzustellen. Wichtige Anwendungsbereiche stellen hierbei die Damascene Technologie, die Abscheidung von Fügeschichten sowie die Metallisierung von Through Silicon Vias (TSV) für die vertikale Integration von Komponenten dar.

Neben der Abscheidung aus wässrigen Elektrolyten wird auch die Abscheidung aus ionischen Flüssigkeiten untersucht. Der Fokus liegt dabei derzeit auf der Aluminium Abscheidung für Anwendungen als Leitungsmaterial in der Mikroelektronik, Mikrosystemtechnik und Leiterplattentechnik. Das Fraunhofer ENAS beherrscht die Aluminiumabscheidung auf 150-mm Wafer auf unterschiedlichen Startschichten (Al, Cu, Au, Pt) und hochdotiertem Silizium. Das Aluminium kann als elektrisch und thermisch leitendes Material sowie als Fügeschicht für Wafer- und Chip-Level Fügeprozesse verwendet werden.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme