Elektroformierungsfreie Memristoren für disruptive Innovationen in KI–Hardware-Architekturen

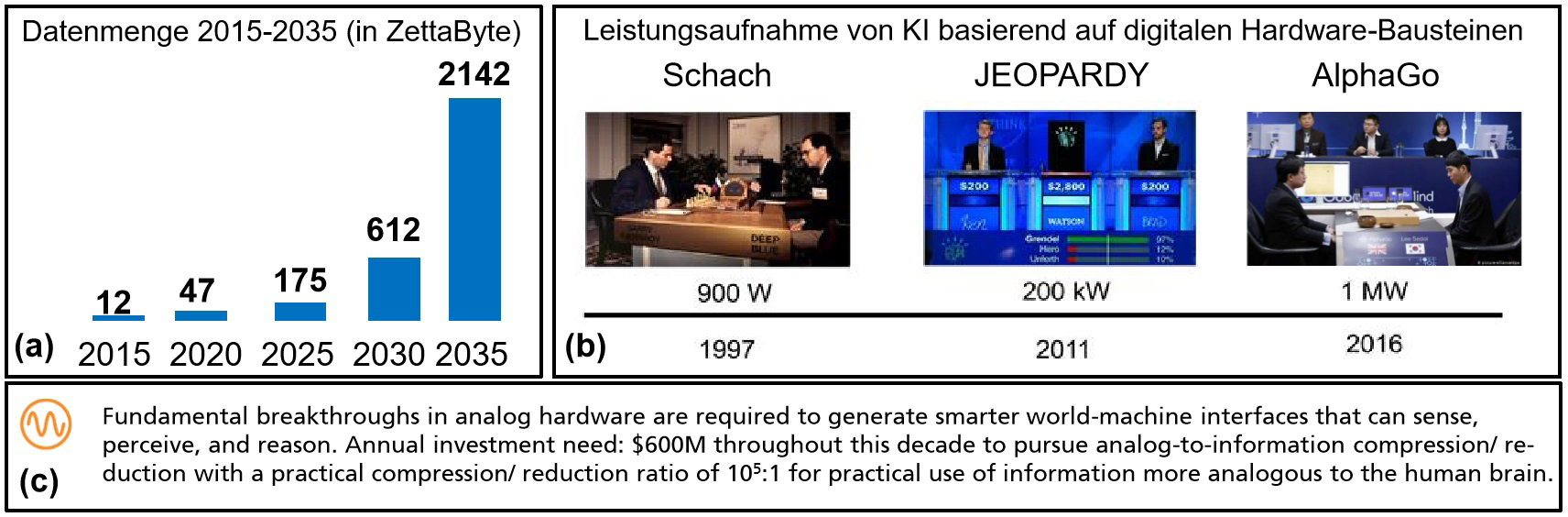

KI mit klassischen, auf der Silizium-Technologie beruhenden, digitalen Hardware-Bausteinen stößt bezüglich Latenz, Genauigkeit, Platzbedarf, Datendurchsatz (Abb. 1a), Energieeffizienz (Abb. 1b), CO2-Footprint und Lernrate an Grenzen, die sich auch durch die Weiterentwicklung von Software nicht oder nur mit äußerst großem Aufwand überwinden lassen werden. Die Dimension dieser Herausforderung wird in der neuesten Roadmap der Semiconductor Research Corporation beschrieben1 (Abb. 1c). Es fehlen elektroformierungsfreie, analoge und digitale KI-Hardware-Bausteine. Dank der von uns entwickelten, elektroformierungsfreien KI-Hardware-Bausteine BiFeO3 (BFO)-Memristor und YMnO3 (YMO)-Memristor werden neue KI-Hardware-Architekturen möglich und wird das Potenzial für eine kaum abschätzbar große Zahl an auf dieser KI-Hardware basierenden, disruptiven Innovationen geschaffen. Wir greifen auf eine spezifische Infrastruktur, Kooperationspartner und Kompetenzen mit Alleinstellungscharakter zurück: Dies umfasst als Technologie-Anwender KMUs und Startups in Deutschland sowie die ortsansässige, in Europa einmalige, sächsische Halbleiterindustrie, die mit ihren Strukturgrößen – Globalfoundries 22 nm - über den erforderlichen Maschinenpark zur Herstellung verfügen. Dazu kommen die Forschungsfabrik Mikroelektronik Deutschland, Software- und Hardware-Testbeds (TU Dresden, TU Chemnitz, Fraunhofer ENAS) sowie Wissenschaftler aus universitären und außeruniversitären Forschungseinrichtungen, welche in der Materialforschung für KI-Hardware sowie im Schaltungsdesign und -aufbau und in der KI-Software-Entwicklung ausgewiesen sind. Derzeit entwickeln wir in Referenz-Projekten auf Demonstrator-Ebene KI-Hardware-Architekturen mit elektroformierungsfreien Memristoren für die Sensornahe Datenverarbeitung sowie für die Vertrauenswürdige Elektronik.

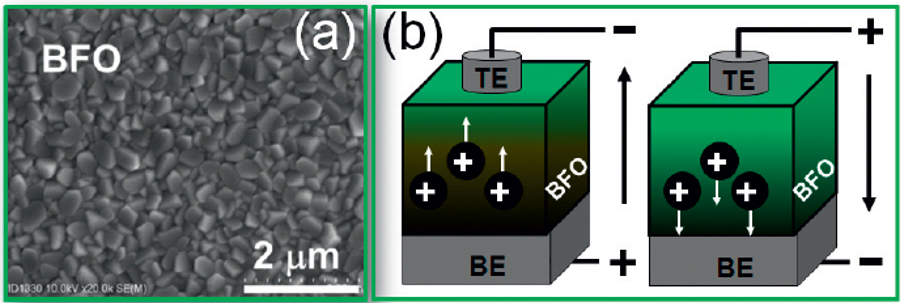

Da Memristoren in hochskalierbaren KI-Schaltungen typischerweise in einer Crossbar-Struktur angeordnet werden, ist grundsätzlich anzustreben, elektroformierungsfreie Memristoren zu nutzen, da sonst die Fehleranfälligkeit steigt. Der elektroformierungsfreie BiFeO3(BFO)-Memristor (Abb. 2) weist alle notwendigen Eigenschaften des fehlenden analogen KI-Hardware-Bausteines auf. Der Elektroformierungsschritt wird in Crossbar-Strukturen mit BFO-Memristoren vermieden und ermöglicht neben der Realisierung der analogen Datenverarbeitung auch die analoge Datenspeicherung als einzigartige Funktionalität in hochskalierbaren KI-Schaltungen. Darüber hinaus sind BFO-Memristoren aufgrund ihrer hohen Variabilität in der Herstellung zur Verwendung als PUF-Krypto-Elemente (Physical Unclonable Function- PUF) in der Vertrauenswürdigen Elektronik geeignet.

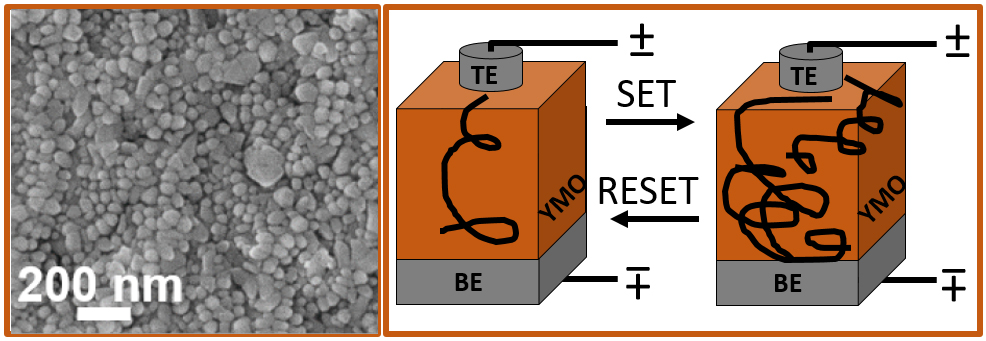

Der elektroformierungsfreie YMO-Memristor (Abb. 3) weist alle notwendigen Eigenschaften des fehlenden digitalen KI-Hardware-Bausteines auf und ist aufgrund seiner hohen Entropie zur Verwendung als RNG-Krypto-Element (Random- Number Generator – RNG) geeignet.

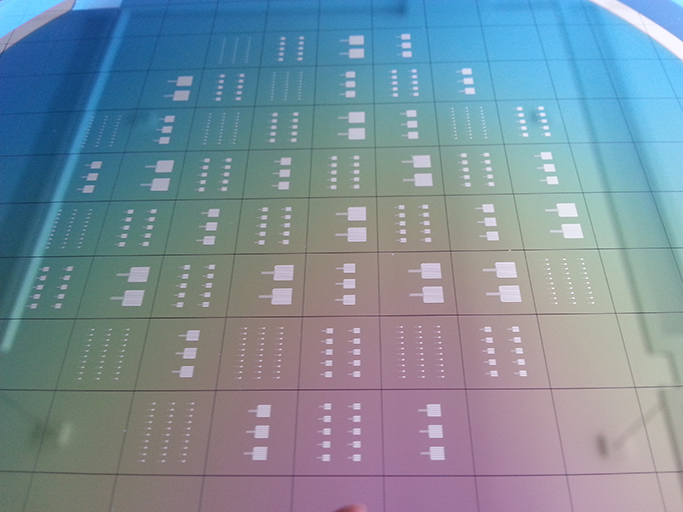

Basierend auf den elektroformierungsfreien Memristoren entwickeln wir die Technologie (Abb. 4) zur Herstellung innovativer KI-Hardware-Architekturen für die Sensornahe Datenverarbeitung und für die Vertrauenswürdige Elektronik. Das ist der Beginn des 1. Seismic Shifts »The Analog Data Deluge«1 (Abb. 1c) und stellt eine neu hinzukommende Stufe der Wertschöpfung dar, was zu neuen Wertschöpfungspotenzialen auf Seiten der Anwendungen von Mikroelektronik und entlang ihres Herstellungsprozesses führt.

1) Five Seismic Shifts That Will Define The Future of Semiconductors and ICT, www.src.org/about/decadal-plan/

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme