Simulation der Abscheidung von Barriere-Saatschicht-Stapeln für die Metallisierung von 28 nm CMOS Devices

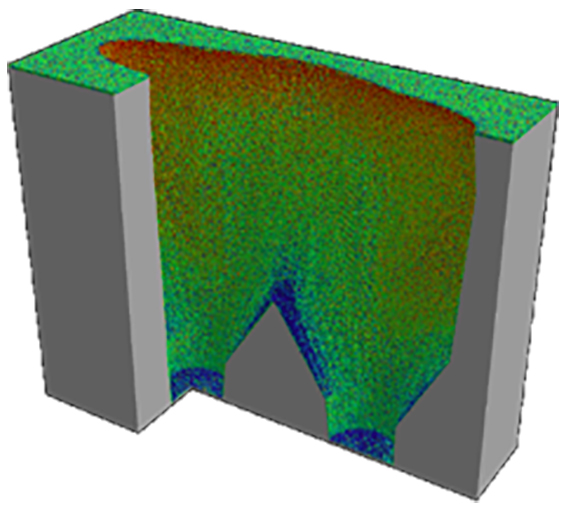

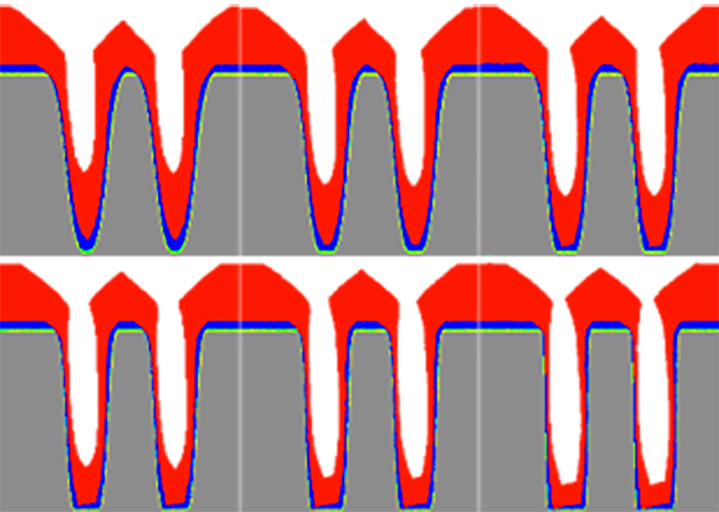

Mit der zunehmenden Miniaturisierung in der Mikroelektronik ergeben sich neue Herausforderungen für die Abscheidung ultradünner Schichten mittels physikalischer Gasphasenabscheidung (PVD). Schmale Gräben und Vias mit hohem Aspektverhältnis sowie Schichtdicken im einstelligen Nanometer-Bereich über den gesamten Wafer erfordern eine präzise Kontrolle der Schichtdicke. Das Fraunhofer ENAS hat ein umfangreiches hauseigenes Softwarepaket entwickelt, mit dem jeder Aspekt der PVD simuliert und optimiert werden kann, von der atomistischen Oberflächeninteraktion bis zum Partikeltransport im Reaktor. Neuentwicklungen ermöglichen die PVD-Simulation auf bis zu 1 µm großen Oberflächenstrukturen mit Schichtauflösungen im Sub-Nanometer-Bereich sowie die Unterstützung moderner Hochleistungs-Rechner. Damit ist es am Fraunhofer ENAS möglich, den vollständigen Prozess der Barriere-Saatschicht-Abscheidung, wie etwa das TaN-Ta-Cu-System, zu untersuchen und hinsichtlich der Abscheidedauer, des Ressourcenverbrauchs und der Zuverlässigkeit zu optimieren. Im Projekt EVOLVE werden gemeinsam mit dem Chiphersteller GLOBALFOUNDRIES diese Simulationen genutzt, um Abscheideparameter für Barriere-Saatschichten zu identifizieren, die für alle 28 nm CMOS-Strukturen auf dem Wafer gleichermaßen gute Beschichtungen liefern.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme