Memristoren für die Rechner von Morgen

![BFO-Memristor mit Vorderseitenelektrode und Rückseitenelektrode mit komplementär rekonfigurierbaren Barrierenhöhen zur (a) digitalen und (b) analogen Datenverarbeitung. (a) Die komplementären, digitalen Widerstände (PLRS, PHRS) und (NHRS, NLRS) werden in Abhängigkeit von den beiden Logikinput-Variablen (Polarität der Schreibspannung Uwrite, Polarität der Lesespannung Uread ) definiert. (b) Die komplementären, analogen Widerstandszustände (LTP, LTD) und (anti-LTP, anti-LTD) werden in Abhängigkeit von den beiden Logikinput-Variablen (Polarität des Zeitversatzes t, Polarität der an der Vorderseitenelektrode und der Rückseitenelektrode angelegten Schreibspannung) definiert. Der logische Zustand (a) ‚0‘ oder ‚1‘ und (b) [0…1] bleibt nichtflüchtig im BFO-Memristor gespeichert. BFO-Memristor mit Vorderseitenelektrode und Rückseitenelektrode mit komplementär rekonfigurierbaren Barrierenhöhen zur (a) digitalen und (b) analogen Datenverarbeitung. (a) Die komplementären, digitalen Widerstände (PLRS, PHRS) und (NHRS, NLRS) werden in Abhängigkeit von den beiden Logikinput-Variablen (Polarität der Schreibspannung Uwrite, Polarität der Lesespannung Uread ) definiert. (b) Die komplementären, analogen Widerstandszustände (LTP, LTD) und (anti-LTP, anti-LTD) werden in Abhängigkeit von den beiden Logikinput-Variablen (Polarität des Zeitversatzes t, Polarität der an der Vorderseitenelektrode und der Rückseitenelektrode angelegten Schreibspannung) definiert. Der logische Zustand (a) ‚0‘ oder ‚1‘ und (b) [0…1] bleibt nichtflüchtig im BFO-Memristor gespeichert.](/de/geschaeftsfelder/micro_and_nanoelectronics/Beyond-CMOS-und_HF-Bauelemente/Memristoren_fuer_die_Rechner_von_morgen/jcr:content/contentPar/sectioncomponent/sectionParsys/textwithinlinedimage/imageComponent1/image.img.jpg/1627470183339/BFO-Memristor-mit-Vorderseitenelektrode-und-Rueckseitenelektrode-mit-komplementaer-rekonfigurierbaren-Barrierenhoehen-512px.jpg)

Angesichts der zunehmenden Herausforderung bei der Miniaturisierung von konventionellen CMOS-Schaltkreisen für Rechner in der von-Neumann-Architektur mit räumlich getrennter Datenverarbeitung und -speicherung, ist eine weitere Leistungssteigerung durch Miniaturisierung perspektivisch ökonomisch kaum mehr vertretbar. Im weltweit voranschreitenden Digitalisierungsprozess wird deshalb auch an neuen elektronischen Bauelementen und Architekturen für die Rechner von morgen geforscht. Derartige Rechner vereinen Datenverarbeitung und -speicherung an einem Ort und ermöglichen energieeffizientes maschinelles Lernen, neuromorphes Rechnen und Datenverschlüsselung am Ort der Datenentstehung. Eines der wichtigsten neuen Zweitor-Bauelemente, der sogenannte Memristor, ermöglicht Datenverarbeitung und -speicherung an einem Ort. Memristor ist ein Kunstwort aus Memory und Resistor.

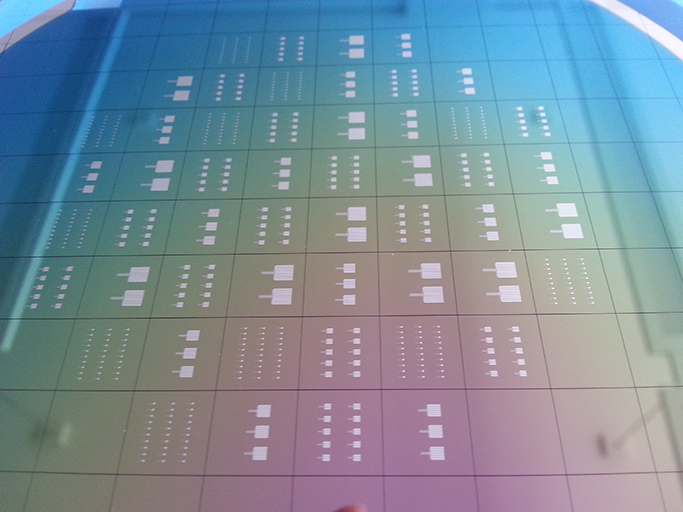

Wir haben am Fraunhofer ENAS gemeinsam mit dem Helmholtz-Zentrum Dresden-Rossendorf einen Memristor auf der Basis von BiFeO3 entwickelt, welcher sowohl digitale und analoge Datenspeicherung als auch digitale und analoge Informationsverarbeitung (Abb. 1) ermöglicht. Derzeit entwickeln wir am Fraunhofer ENAS im Rahmen des ATTRACT-Projektes »Entwicklung einer Gesamttechnologie für die modulare Integration neuartiger elektronischer Bauelemente in mikroelektronische CMOS-Hybride - BFO4ICT« eine Technologie zur Herstellung des BiFeO3 (BFO) auf Wafer-Niveau und implementieren die Fertigung von BFO-basierten Memristoren in konventionelle industrielle Prozessabläufe. Die Widerstandseigenschaften von BFO-Memristoren lassen sich durch einen Spannungs- oder Stromschreibpuls nichtflüchtig schreiben und mit einem kleinen Spannungs- oder Stromlesepuls auslesen. Beim Schreiben der BFO-Memristoren werden die Barrierenhöhen der Vorderseiten-Elektrode und der Rückseiten-Elektrode rekonfiguriert und damit die Diodeneigenschaften der BFO-Memristoren nichtflüchtig und analog geändert.

Für viele avisierte Anwendungen von Memristoren in Rechnern von morgen, beispielsweise für das maschinelle Lernen und für das neuromorphe Rechnen, ist eine Anordnung der Memristoren in sogenannten Crossbar-Array-Strukturen vorteilhaft. Typischerweise wird für jeden Memristor in einer Crossbar-Array-Struktur ein Auswahl-Transistor zum Adressieren und zum Vermeiden von Kriechströmen verwendet. Aufgrund der inhärenten Diodencharakteristik von BFO-Memristoren, ist die Anordnung von BFO-Memristoren in Crossbar-Array-Strukturen (Abb. 2) vereinfacht und ohne Auswahl-Transistoren möglich.

Ausgehend vom derzeitigen Wissens- und Technologieentwicklungs-Stand, haben wir im Kapitel „Memristive Technologies“ (H. Schmidt) des White Papers „Implications of Memristor Technologies for Future Computing Systems“ (Eds.: D. Fey, W. Karl, T. Ungerer, Herausgeber: VDE ITG Informationstechnik, 27.06.2019) potentielle Anwendungen für Memristor-Bauelemente mit digitaler und analoger Datenspeicherung und -verarbeitung aufgezeigt und die Herausforderungen für Deutschland und Europa bei der Entwicklung industrietauglicher Technologien zur Herstellung memristiver Bauelemente“ beschrieben. Letztendlich wollen wir auf die in Sachsen und Deutschland vorhandene Industrie, die alle erforderlichen Prozesse und Entwicklungsschritte bereitstellt und auch zukünftig bereitstellen wird, aufsetzen und die Kapazitäten hinsichtlich Herstellungsprozessen, Verfügbarkeit von spezialisierten Technologien, Spezialisten und Know-how, für die Memristor-Bauelemente für Rechner von morgen massiv erweitern.

Fraunhofer-Institut für Elektronische Nanosysteme

Fraunhofer-Institut für Elektronische Nanosysteme