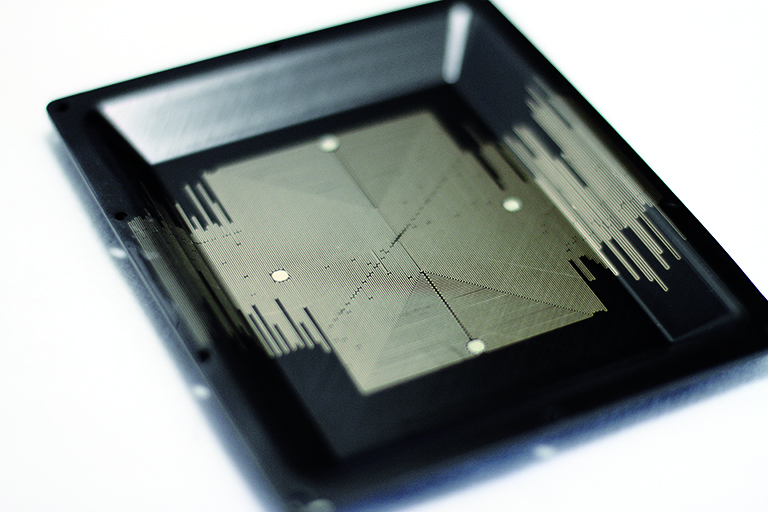

Packaging and (heterogeneous) integration (2D, 2.5D, 3D) for electronic devices

This research and development area focuses on the development of processes for the integration of electronic devices for wafer level packaging, especially joining and contacting processes, thin film encapsulation and screen printing for metallization and solder.

Fraunhofer Institute for Electronic Nano Systems

Fraunhofer Institute for Electronic Nano Systems