Whitepaper on Memristor Technologies

In view of the increasing challenge in the miniaturization of conventional CMOS circuits for computers in the von Neumann architecture with spatially separated data processing and storage, a further increase in performance through miniaturization is in perspective hardly economically justifiable. The Fachbereich Technische Informatik der Informationstechnischen Gesellschaft (ITG) im VDE und der Gesellschaft für Informatik (GI) has published a Whitepaper on memristor technologies: "Implications of Memristor Technologies for Future Computing Systems", Eds.: D. Fey, W. Karl, T. Ungerer, publisher: VDE ITG Informationstechnik, 27.06.2019. Memristor technologies are designed to address the fabrication of new electronic devices and architectures for computers of tomorrow.

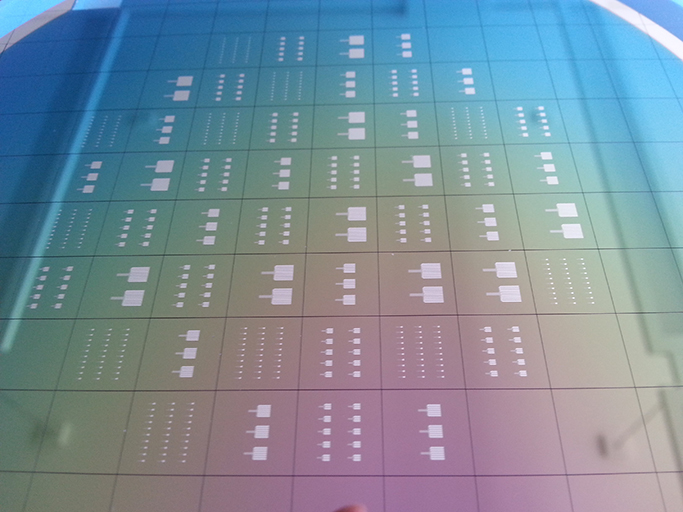

The Fraunhofer Institute for Electronics Nano Systems Fraunhofer ENAS has developed a memristor based on BiFeO3 (BFO) together with the Helmholtz-Zentrum Dresden-Rossendorf, which enables both digital and analogue data storage as well as digital and analogue information processing. Currently, a team at Fraunhofer ENAS is developing a technology for manufacturing BFO waferlevel memristors in crossbar array structures within the framework of the ATTRACT project »Development of an overall technology for the modular integration of novel electronic devices into microelectronic CMOS hybrids - BFO4ICT «. Based on the current state of knowledge and of the technology development of our work, we have shown potential applications for memristor devices with digital and analog data storage and processing in the chapter "Memristive Technologies" (H. Schmidt) of the Whitepaper.

Last modified:

Fraunhofer Institute for Electronic Nano Systems

Fraunhofer Institute for Electronic Nano Systems