On-line stress measurement during manufacturing and in field-testing with the stress chip

A FEM simulation is a well-established method to investigate the reliability of an IC package. The results can predict warpage, residual stresses or remaining lifetime of packages. Nevertheless, these FEM models are always an ideal form without any production tolerances, misalignments or other failures. Many time-consuming tests have to be done to identify, investigate and minimize these statistical realities. The biggest challenge for health monitoring is to find a monitor structure with a strong physics of failure connection. Measuring the current or the temperature inside an electrical package is the simplest way. However, the changes of these values are very weak and late in the behavior of a physical failure. The stress chip can measure little setup and material variations direct without destroying the package. All package components and their production technologies have an impact on the residual stress state of the package. The residual stress is measured at important production steps (naked, die-attach, molding, soldering on a PCB). Finally, a temperature-cycling test with in situ stress measurement is prepared. With newly programmed software is it possible to compare all packages at any stress state. It will be shown the different cycling behavior of the different packages combined with modern AI evaluation technics. These will be fundamental research for the health monitoring of chip packages. But also for a better and faster way for qualification of package technologies because of the faster way of process variations and their impact on the residual stress state of the package.

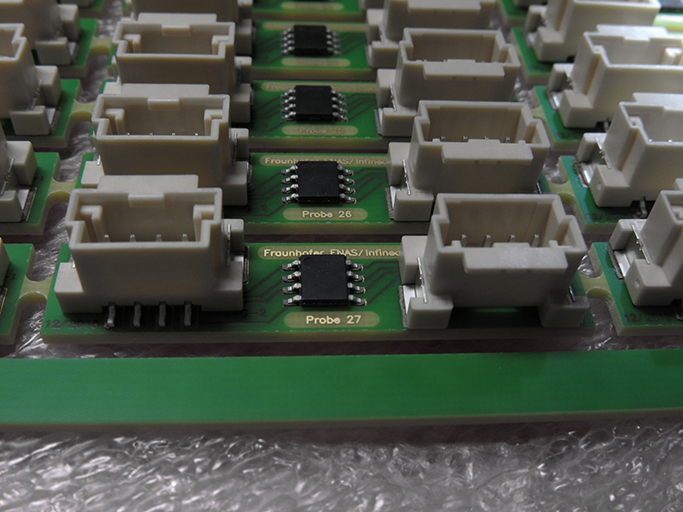

Fraunhofer Institute for Electronic Nano Systems

Fraunhofer Institute for Electronic Nano Systems