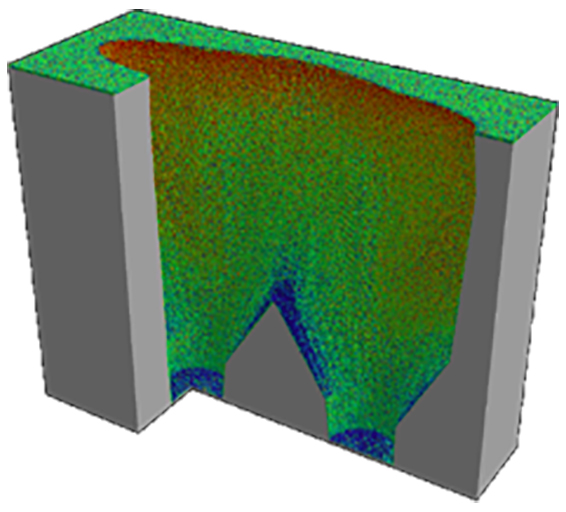

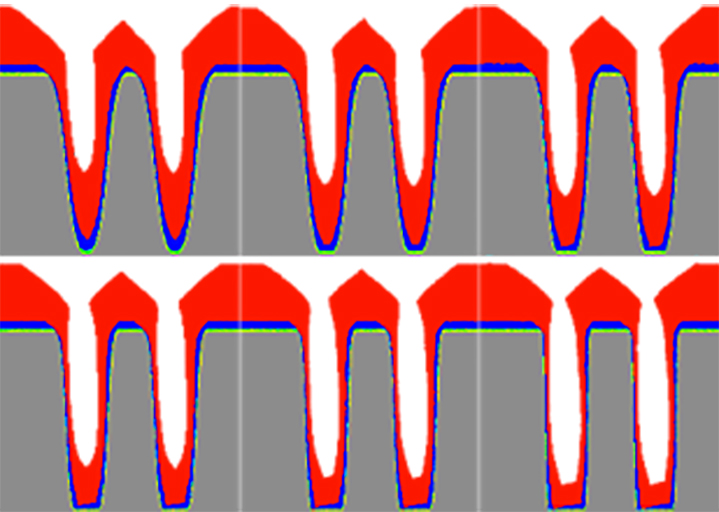

With the ongoing miniaturization of microelectronic devices, new challenges emerge for the production of conformal ultrathin layers using physical vapor deposition (PVD). Narrow trenches, high aspect ratio vias and desired thin films of only a few nanometer thickness across the whole wafer require precise thickness control even on vertical surfaces. At Fraunhofer ENAS, we developed a comprehensive in-house multiscale software suite for the simulation and optimization of every aspect of PVD, from the atomistic surface interactions to the particle transport in the reactor. Recent improvements enable the simulation of PVD on up to 1 µm large surface features with sub-nanometer layer resolution on modern high performance hardware. Through these advancements, we are now able to investigate the full barrier/seed deposition process, such as the TaN-Ta-Cu layer stack, in order to optimize the processes toward time-efficiency, cost-effectiveness and reliability. In the EVOLVE project with the chip manufacturer GLOBALFOUNDRIES, parameters will be identified which yield an optimal barrier/seed deposition process for a wide range of feature geometries in 28 nm CMOS devices.

Fraunhofer Institute for Electronic Nano Systems

Fraunhofer Institute for Electronic Nano Systems