Precise simulation of phase-locked loops for clock and data recovery

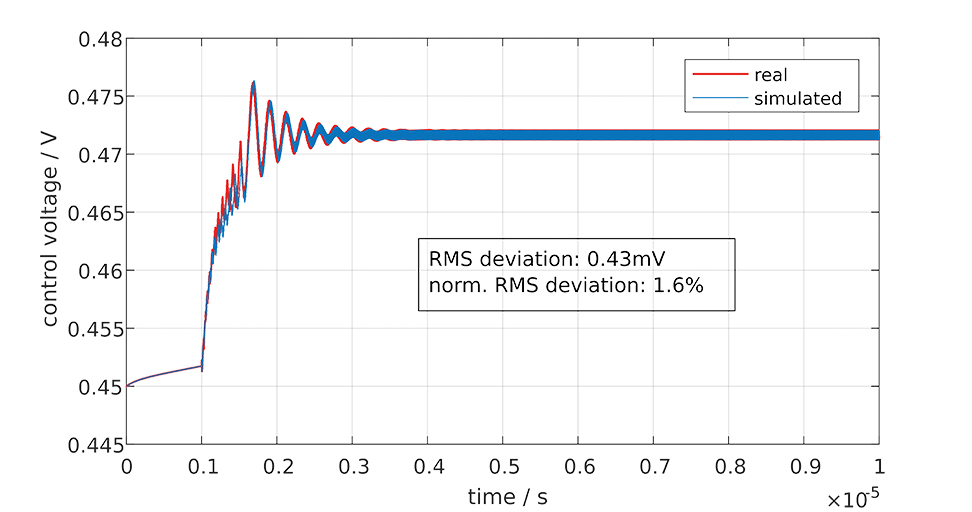

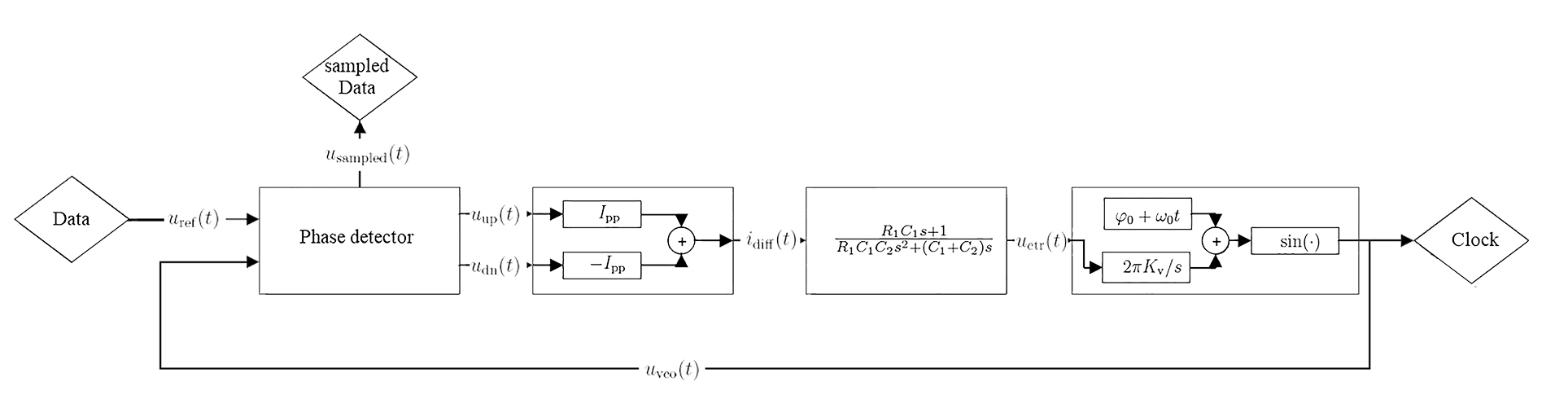

The demand for ever-faster technologies for data transmission is still growing rapidly. The communication systems used for clock and data recovery, such as phase-locked loops (PLL), are required in those asynchronous communication processes. However, the modeling and optimization of these mixed-signal systems is a challenge due to their complex behavior. Based on the method of fully event-driven modelling, a behavioral simulation software has been developed which only calculates its successive switching points by combining analytical and numerical methods. This leads to a higher precision of the simulation with a significantly shorter simulation time. In comparison with common simulators, a speed-up factor of about 10 – 100 is achieved. The modular implementation allows to characterize parasitic and nonlinear effects on system level by Monte-Carlo methods and to optimize the architectures accordingly. In current projects, the software is also used for developing novel receiver systems for 5G applications.

Fraunhofer Institute for Electronic Nano Systems

Fraunhofer Institute for Electronic Nano Systems