# Wafer level packaging based on wafer bonding and TSVs for advanced MEMS integration

**Roy Knechtel** Schmalkalden University of Applied Sciences

Manuela Göbelt X-FAB MEMS Foundry GmbH Erfurt

Prof. Dr.-Ing. R. Knechtel Schmalkalden University of Applied Sciences Autonomous Intelligent Sensors Chair of the Carl-Zeiss-Foundation

Phone: 03683 688-5108 E-Mail: r.knechtel@hs-sm.de

System in Package (SiP) – Package is the integration level widely used – standard, different solutions

**MEMS**

Chip

- + flexible combination of MEMS and CMOS

- form factor rather big and bulky

- distributed supply chain (foundry, assembly house)

SoC is focus of the presentation, how to realize proce

SCHMALKALDE

UNIVERSITY

**CMOS**

Chip

Introduction

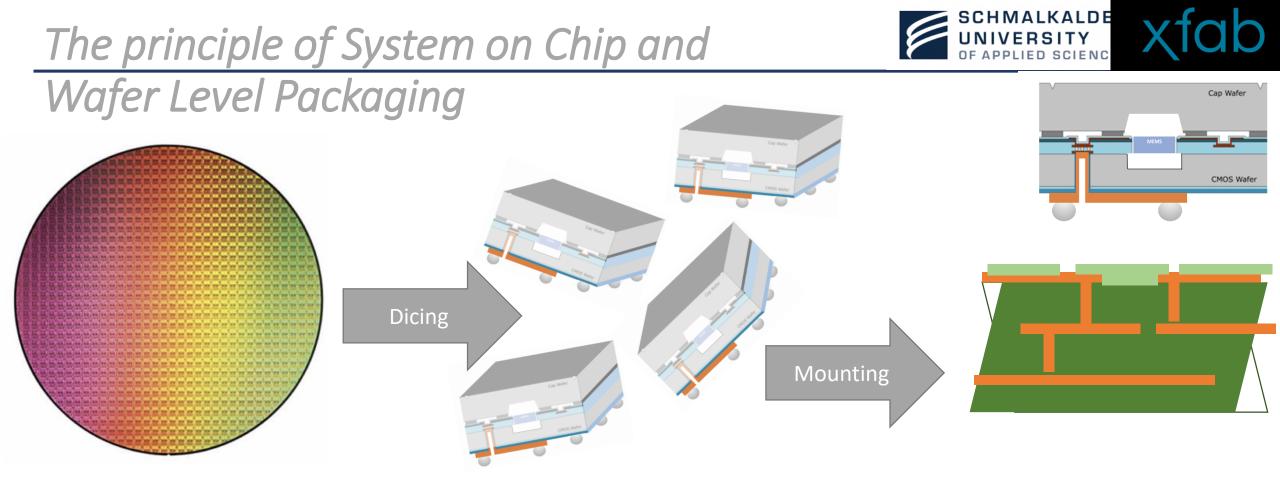

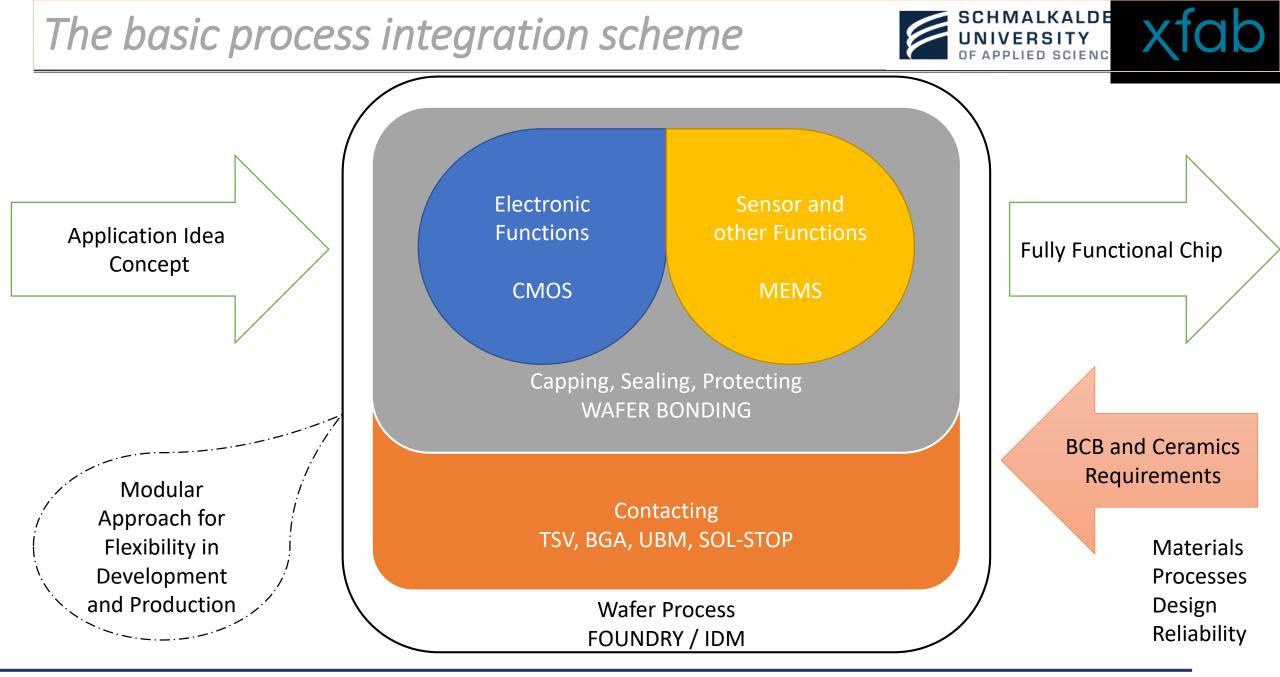

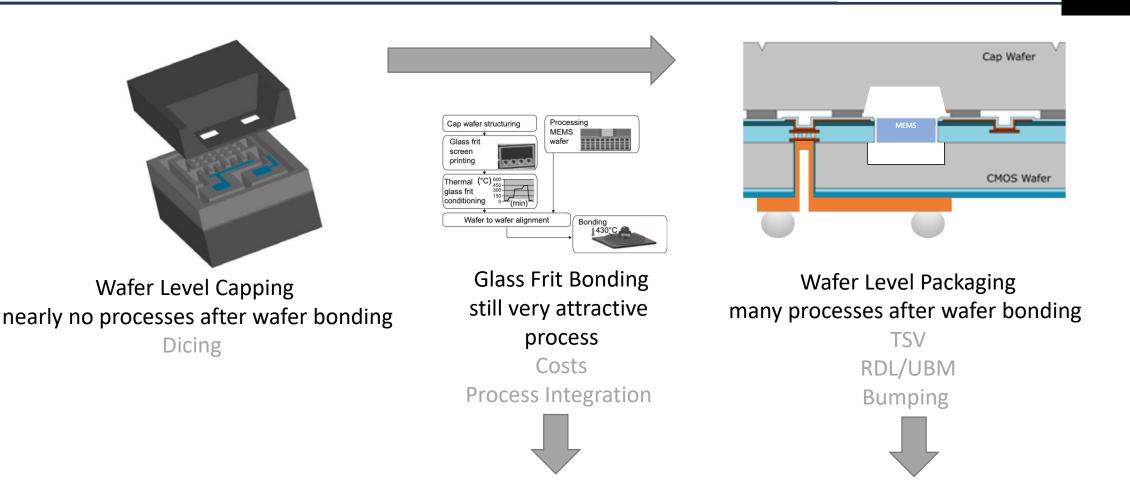

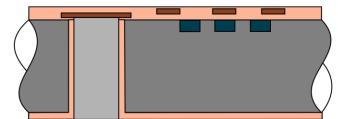

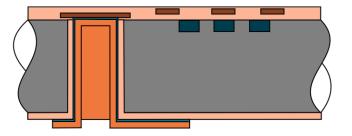

- The principle of System on Chip and Wafer Level Packaging

- The Basic Process Integration Scheme

The Basic Process Modules

- Monolithic Integration of MEMS and CMOS

- Wafer Bonding

- Through Silicon Vias

- Finishing after Wafer TSV Process

An Example of a System on Chip – Chip Scale Package Solutions

Application Aspects and Special Challenges

**Conclusions and Outlook**

SCHMALKALDE

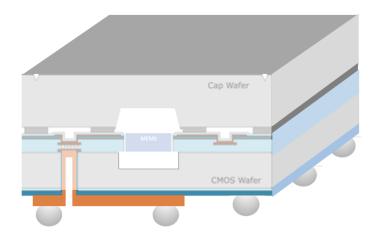

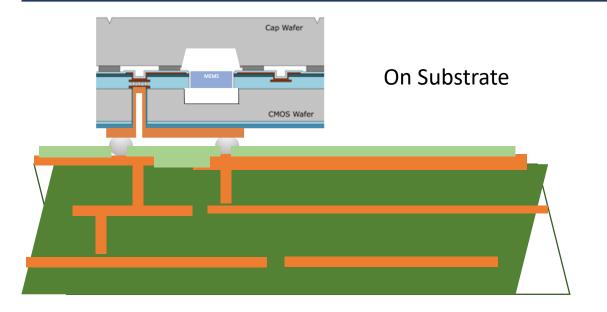

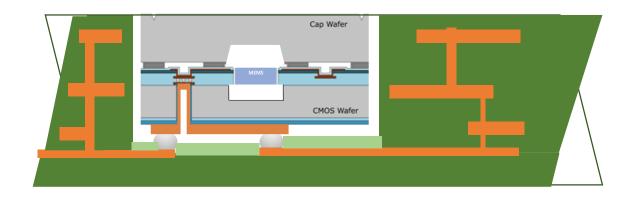

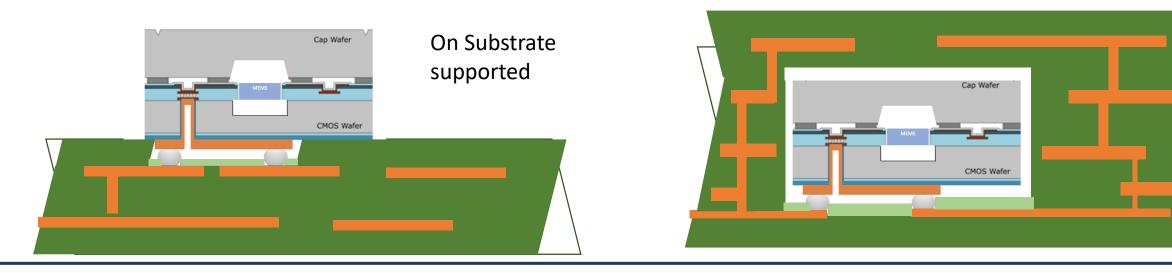

Do *all* the processing on wafer level

- Highest integration

- Parallel processing

- Cost efficient

### Chips directly *ready for mounting on board*

- All functionalities (CMOS, MEMS)

- Solder balls or solder pads

- Passivation and solder stop

- Smallest possible form factor

### Highly integrated bords

- BCB or Ceramics

- Small solutions

Chemnitzer Seminar / 13 Juni 2023 - 14 Juni 202

- High functionality

### June 14th 2023 Prof. Dr.-Ing. R. Knechtel - Schmalkalden University of Applied Sciences, Autonomous Intelligent Sensors, Chair of the Carl-Zeiss-Foundation 5

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023

Electronic Packaging and Applications

**Process Modules**

SCHMALKALDE UNIVERSITY OF APPLIED SCIENC

# ... and how all can fit together

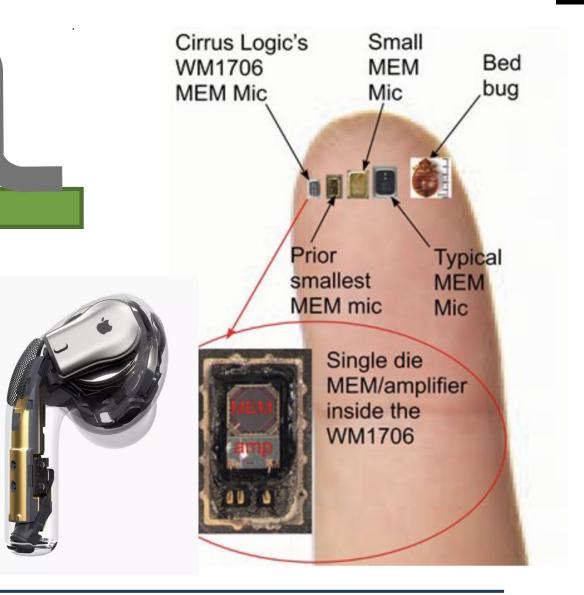

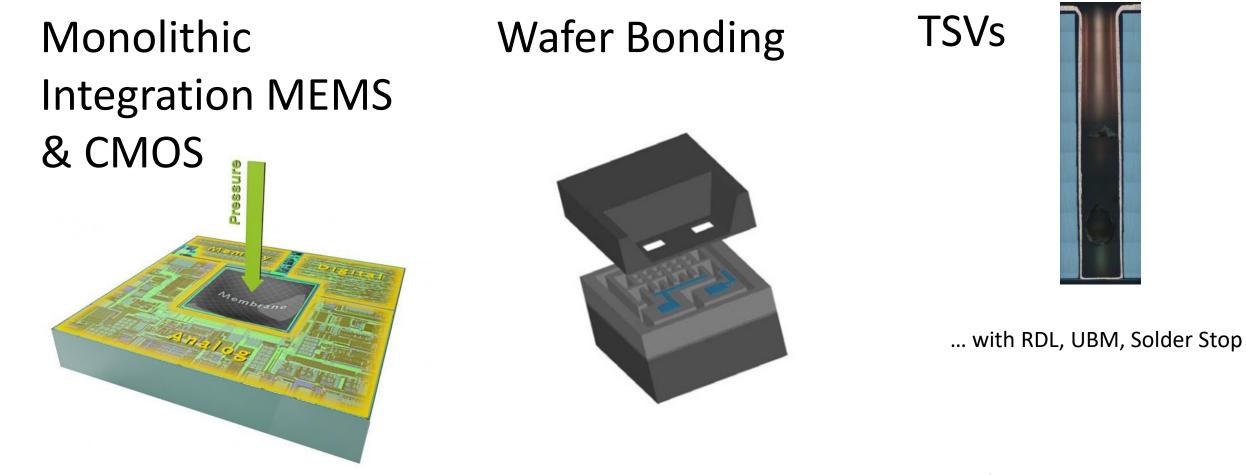

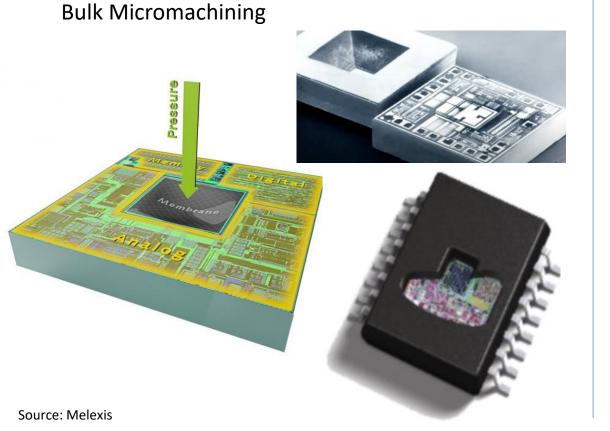

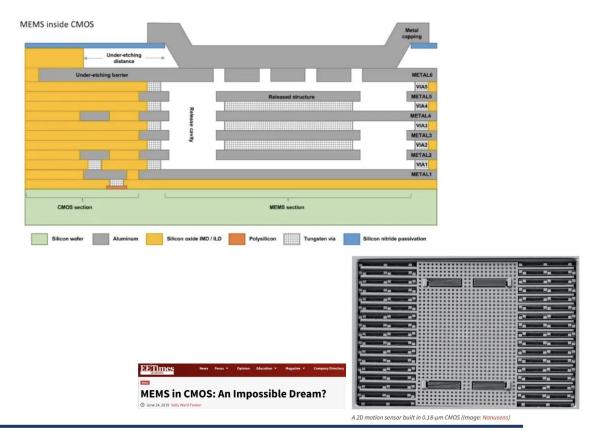

# Monolithic MEMS CMOS Integration

# **MEMS** Devices requires electronics

- Signal processing, sensor signal improving, driving signals,....

- Integration of MEMS ad CMOS on one and the same wafer/chip is well established

### Surface Micromachining

SCHMALKALDE

UNIVERSITY

June 14th 2023 Prof. Dr.-Ing. R. Knechtel - Schmalkalden University of Applied Sciences, Autonomous Intelligent Sensors, Chair of the Carl-Zeiss-Foundation 7

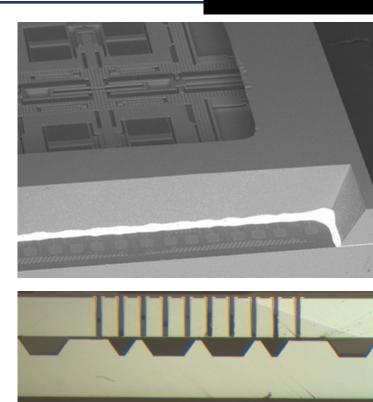

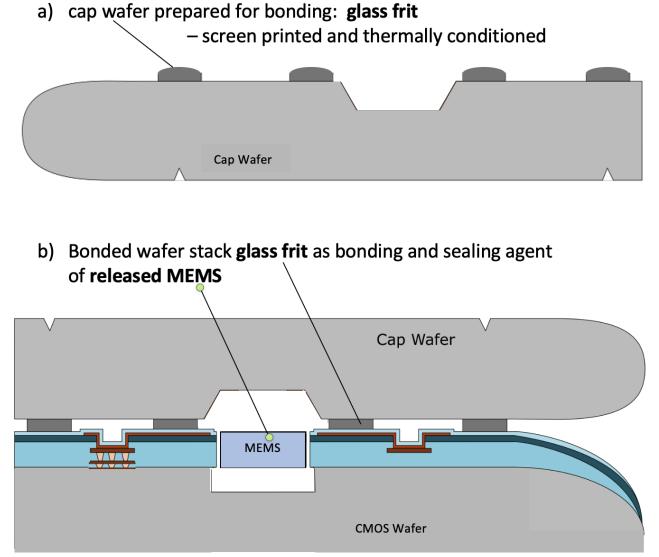

# Wafer Bonding and Process Integration

New requirements Chemical and thermal properties of glass frit materials are important for overall process integration

Maximum process temperatures after glass frit bonding Cleaning processes

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023 Electronic Packaging and Applications

SCHMALKALDE

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023

June 14th 2023 Prof. Dr.-Ing. R. Knechtel - Schmalkalden University of Applied Sciences, Autonomous Intelligent Sensors, Chair of the Carl-Zeiss-Foundation 10

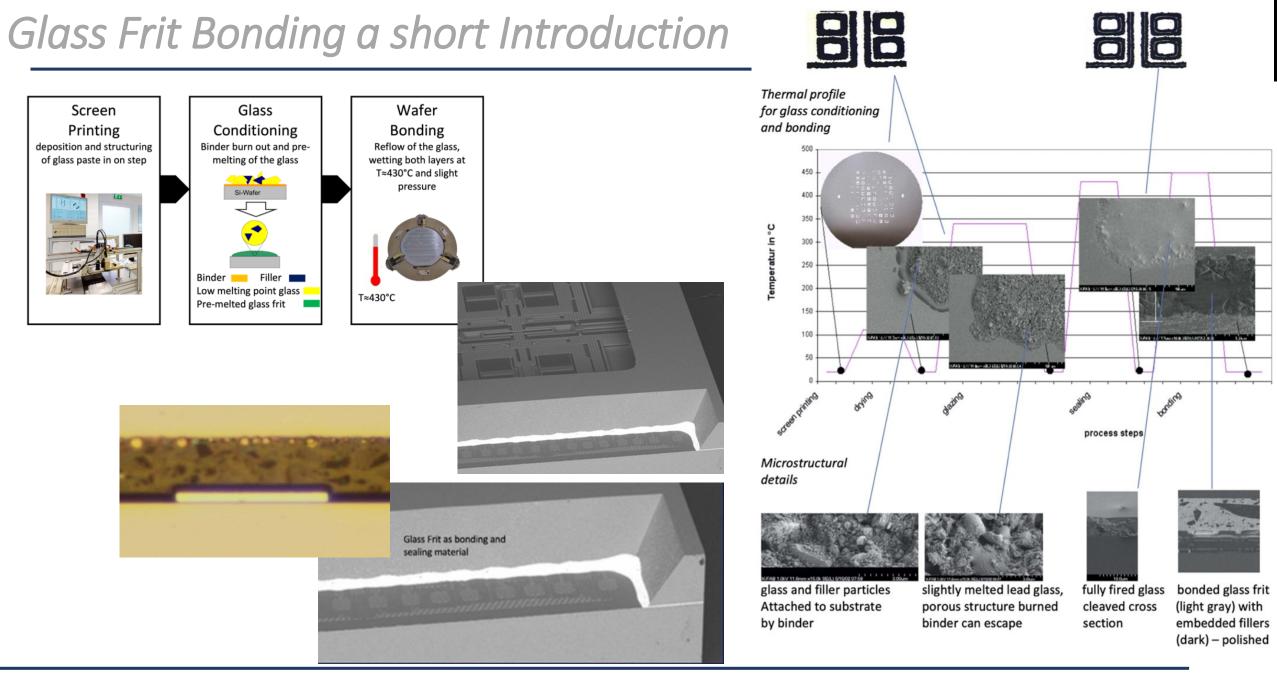

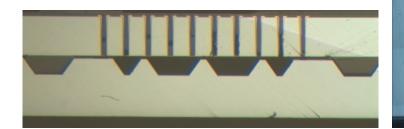

Challenges and Current Developments Glass Frit Bonding

Development of Glass Frit Bonding processes based on lead free materials

Screen Printing – Firing – Bonding – Reliability chemical and electrical properties to be investigated thermo-mechanical properties important - wafer bow

Conflicting requirements for screen printing

Small chips – small bond frames, can lead to high amount of paste covered areas - problems in release of the screen – different optimizations (screen and process) are necessary

Optimal bonding process – time, peak temperature, wafer bow, hermeticity / bonding strength

Fraunhofer

In Wafer Process special configurations are required, such as:

- chip and wafer edge sealing

- small edge exclusion zone

- thermal and chemical glass frit stability

... mostly related to wafer bonding.

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023

# Wafer Bonding with Electrical Contacting

**ENAS**

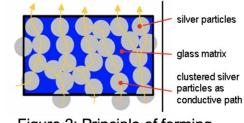

### **Conductive Glass Frit Bonding**

Figure 1: SEM images silver filled conductive glass frit

Figure 2: Principle of forming conductive paths in the frit

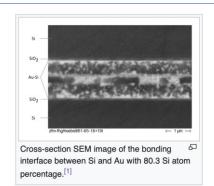

## Eutectic Bonding

Lin, Y.-C.; Baum M.; Haubold, M.; Fromel J.; Wiemer, M.; Gessner T.; Esashi, M. (2009). "Development and evaluation of AuSi eutectic wafer bonding". *Solid-State Sensors, Actuators and Microsystems Conference, 2009. TRANSDUCERS 2009. International.* pp. 244– 247. <u>doi:10.1109/SENSOR.2009.5285519</u>

### NT A ISP MC Cu ISP ILD 7.4 SO CIS MC Cu CIS MC CU

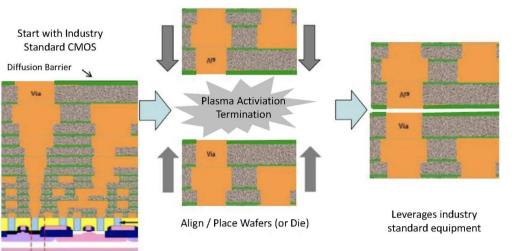

### Hybride Wafer Bonding

Ziptronix Cu-Cu / Oxide "hybrid bonding" Process Flow (Source: Permanent Wafer Bonding, Yole Développement, May 2014)

http://image-sensorsworld.blogspot.com/2020/10/hybrid-bondingreview.html

| Via First<br>TSV Etch      | TSV Fill    | High Temp FE | Low Temp BE | Wafer Thin |

|----------------------------|-------------|--------------|-------------|------------|

| Via Middle<br>High Temp FE |             | TSV Fill     | Low Temp BE | Wafer Thin |

| Via Last<br>High Temp FE   | Low Temp BE | Wafer Thin   | TSV Etch    | TSV Fill   |

Via First: before device fabrication

- $\rightarrow$  Difficult process integration

- ightarrow Interactions with CMOS parameters

Via Middle: before metal line fabrication

- $\rightarrow$  Difficult process integration

- ightarrow Interactions with CMOS parameters

Via Last: after metal line fabrication

- → Independent from CMOS process

- → Independent process module

- $\rightarrow$  Universally applicable

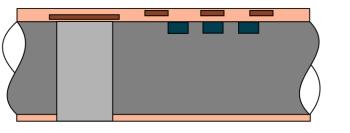

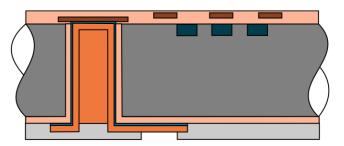

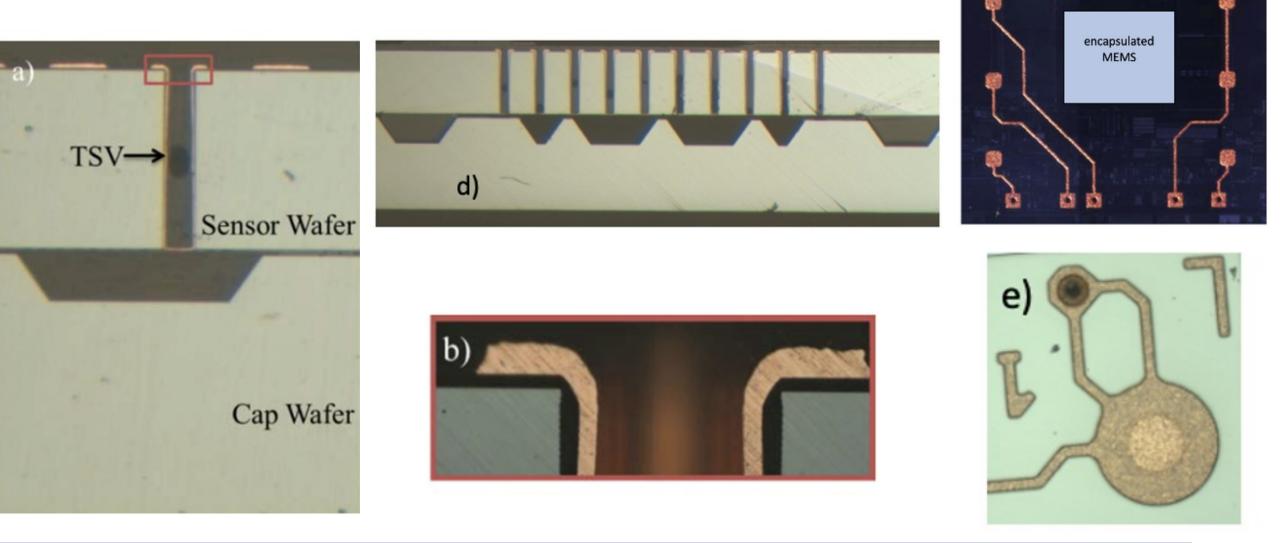

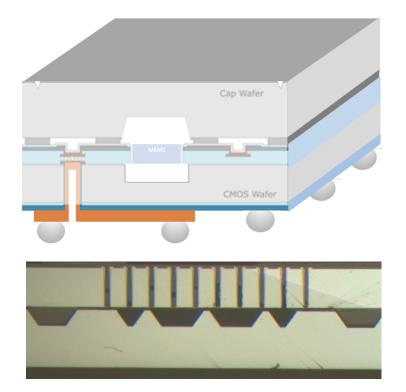

# **TSV Process**

Wafer abdünnen & Ätzen der TSVs

Galvanisches Cu & Entfernen B/S

Passivierung der TSVs

Abscheidung Barrier- und

Saat-Schicht (B/S)

Last process step of TSV is copper metallization, but this not solderable

Under Bump Metallization (UBM) is required...

Nickel and Gold

E-less plated or sputtered (Lift off)

... and Solder Stop Layer (SolStop)

Polymers

Oxide/Nitride...

### Example e-less Ni/Au at Polymer Passivation

CHMALKALDE

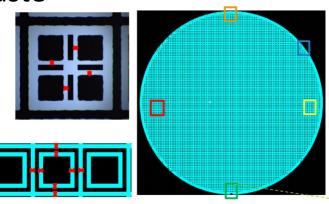

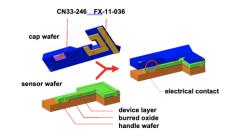

An example of a System on Chip Chip Scale Package Solutions

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023 Electronic Packaging and Applications

SCHMALKALDE UNIVERSITY OF APPLIED SCIENC

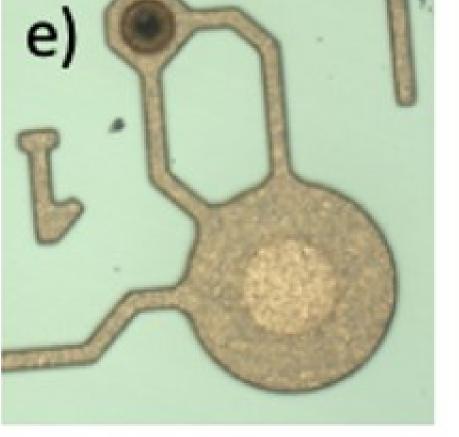

c)

# **Applications Aspects**

SCHMALKALDE UNIVERSITY OF APPLIED SCIENC

### Embeded

### Included / Protected

Chemnitzer Seminar / 13. Juni 2023 - 14. Juni 2023

Electronic Packaging and Applications

### Wafer process

- Overall **technology integration** (e.g., thermal & chemical stability of glass frit bonding during TSV process)

- Preparation of solder process (solder balls size, material and process; just solderable pads?)

- Temperature limitation (T > 250°C has influence on Cu grain growth)

- Passivation material (hard or soft, hydrophobic)

- **Dicing** of bonded wafer stack with hidden CMOS

- Supply chain (longer wafer process, but no assembly process)

- Follow up of commodity products (smaller CSP out of standardization)

- Shipment forms (e.g., on trays, tape on reel)

### **Board or ceramic mounting**

- **Total temperature budget** to be considered (soldering temperature, 5x reflow, low temp. solder required?)

- Does board mounting provide some **protection** (embedded, included, underfill, glob top?)

- Thermal mechanical stress (operating temperature, thermal cycles and shocks)

- Co-design of boards and chips (bridging critical dimensions)

- Reliability

- Cost structures no assembly, but higher wafer and board costs

Chip scale packaged, system on chip solutions are becoming reality. They are providing extreme high integration densities - in themselves, but also for ceramic or BCB solutions (smallest possible from factor).

For such complex and highly integrated systems on chip, realized in wafer processes and without any single die assembly, different process blocks

- (glass frit) wafer bonding

- TSV

- RDL, UBM, SolStop, Solder

... need to be combined and adapted to each other (process integration).

There are quite some challenges in number, but rather work to be done until all details are fitting together.

For sure, the chances of such solutions are dominating the challenges.

Roy Knechtel thanks the Carl-Zeiss-Foundation for the funding his professorship.

Thank you for your Attention!

# l'm open for your questions.

SCHMALKALDE UNIVERSITY

D SCIENC